운동하는 공대생

[OS(운영체제)] TLB (Translation Lookaside Buffer) 본문

1. Problem

이전에서 설명을 했지만 VA에서 PA로 주소를 변환하는 과정이 굉장히 많은 비용이 발생한다. 그래서 이런 방식은 시간이 많이 걸리고 또한 linear 한 단순한 방식이 아닌 multi-level page table 방식 같은 경우에는 더 많은 시간이 소요된다.

2. TLB (Translation Lookaside Buffer)

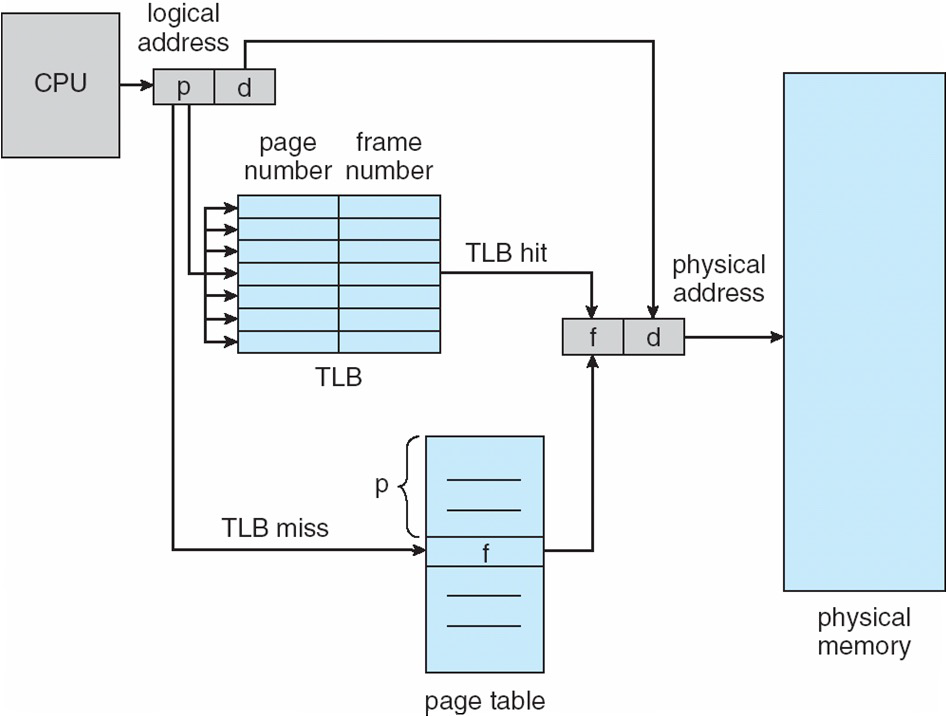

문제에서 이야기를 했듯이 translation 시간을 빠르게 하기 위해서 MMU안에 TLB라는 cache 하드웨어가 존재한다.

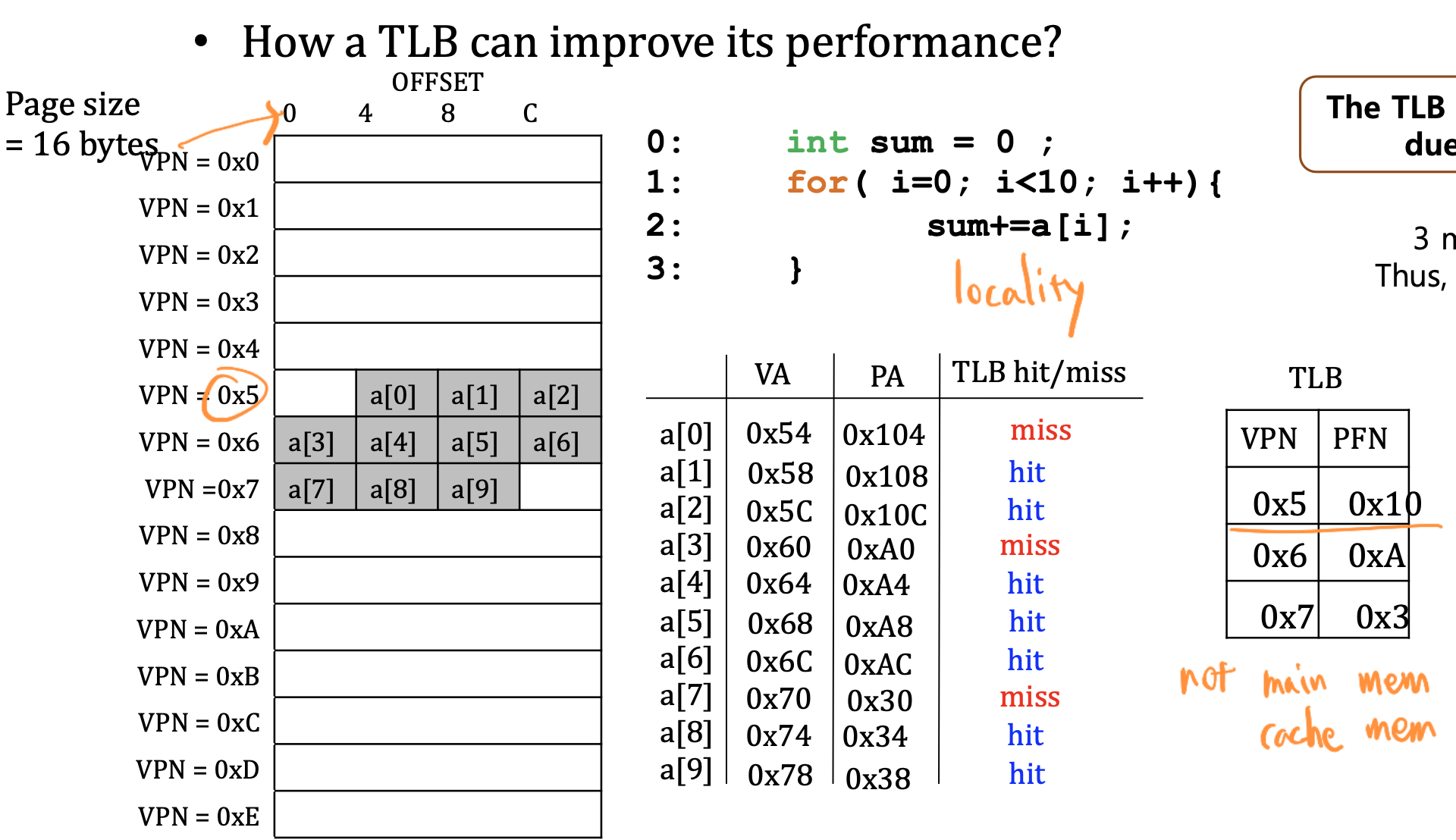

위에 나온 사진을 보면 먼저 offset이 4비트로 표현된 16 bytes의 크기의 page로 구성이 되어진다고 할 때 페이지의 주소를 PA로 변환하면 page table에 의하여 변환이 될 것이다. 하지만 여기서 VPN은 같고 offset의 차이만을 가지고 연산을 진행하는 경우에는 같은 PA의 앞 주소가 나오는 현상이 있음으로 이것을 cache에 저장하여 조금 더 빠르게 연산이 가능하도록 한 방식이다.

이 특징을 활용이 가능한 이유는 메모리에 대한 Locality특성 때문에 가능하다.

- Temporal Locality : 최근에 접근한 데이터는 또 접근할 가능성이 높다.

- Spatial Locality : 공간적으로 비슷한 위치에 존재한다면, 근처에 먼저 접근한다면 그 근처로 접근할 가능성이 높다.

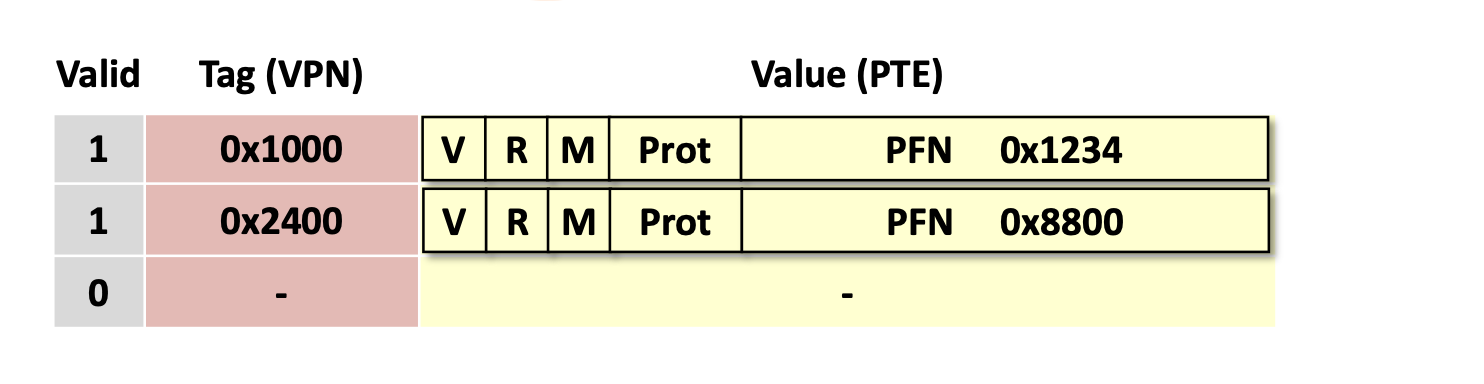

TLB는 먼저 cache 이기 때문에 cache의 특성을 가지고 있는데 여기서 16~256개의 entries를 가지고 있으며 LRU알고리즘을 통해서 데이터를 관리한다. 또한 위의 사진처럼 VPN과 PFN 만을 가지고 있는게 아니라 PTE의 모든 요소를 다 가지고 있다. 그리고 VPN이 TLB에 모든 entry와 접근이 가능한 fully associative한 형식을 가진다.

3. Handling TLB

3.1 TLB Misses

- Software-managed TLB : OS가 cache miss를 탐지하고 관리한다. 즉 TLB에 알맞은 PTE를 OS가 찾아오고 이는 유동적인 관리가 가능하다.

- Hardware-managed TLB : CPU가 페이지 테이블의 저장 위치를 알고 있으며 하드웨어가 관리를 한다.

3.2 TLB on Context Switches

기본적으로 TLB는 Context Switch 상황에서 Flush를 모두 날리는 방식을 사용한다. 하지만 특정 아키텍처(MIPS, Intel)에서는 이런 TLB를 남겨 두기도 한다. TLB 엔트리는 ASID를 통해서 관리되며 어떤 프로세스의 TLB entry인지 구분한다.

'OS' 카테고리의 다른 글

| [OS(운영체제)] Virtual Memory Swapping (0) | 2024.08.29 |

|---|---|

| [OS(운영체제)] Concurrency: Locks (2) | 2024.08.28 |

| [OS(운영체제)] Advanced Page Tables (0) | 2024.08.26 |

| [OS(운영체제)] Paging (0) | 2024.08.26 |

| [OS(운영체제)] Virtual memory Address translation (0) | 2024.08.23 |